java

python爬虫兼职

嵌入式Linux SPI驱动

子图

system

题集

dirs 命令

Tableau

文字

数字化

DDPM

Nanoprobes

游戏开发

web前端

shell 实现

hevc

coinbase

设置默认浏览器

强化学习

网页模版html

FIFO

2024/4/11 21:02:56Designing_With_EZ-USB_FX2LP_Slave_FIFO_Interface-Source Code_Verilog——Stream Out

(1)fx2lp_slaveFIFO2b_streamOUT_fpga_top.v

module fx2lp_slaveFIFO2b_streamOUT_fpga_top(fdata, // FIFO data lines.faddr, // FIFO select lineslrd, // Read cont…

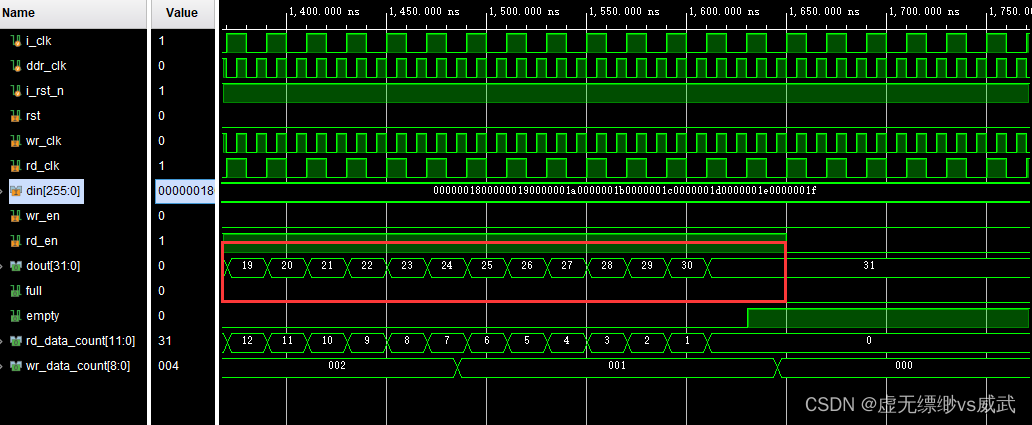

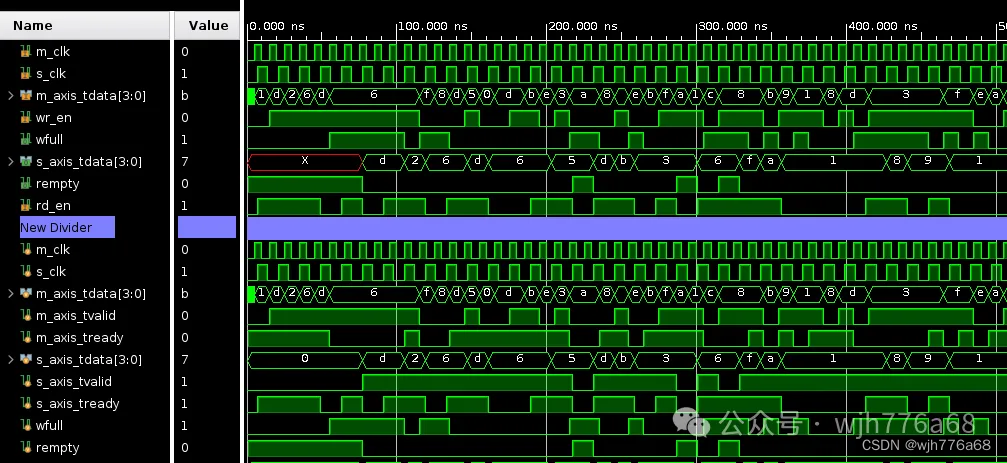

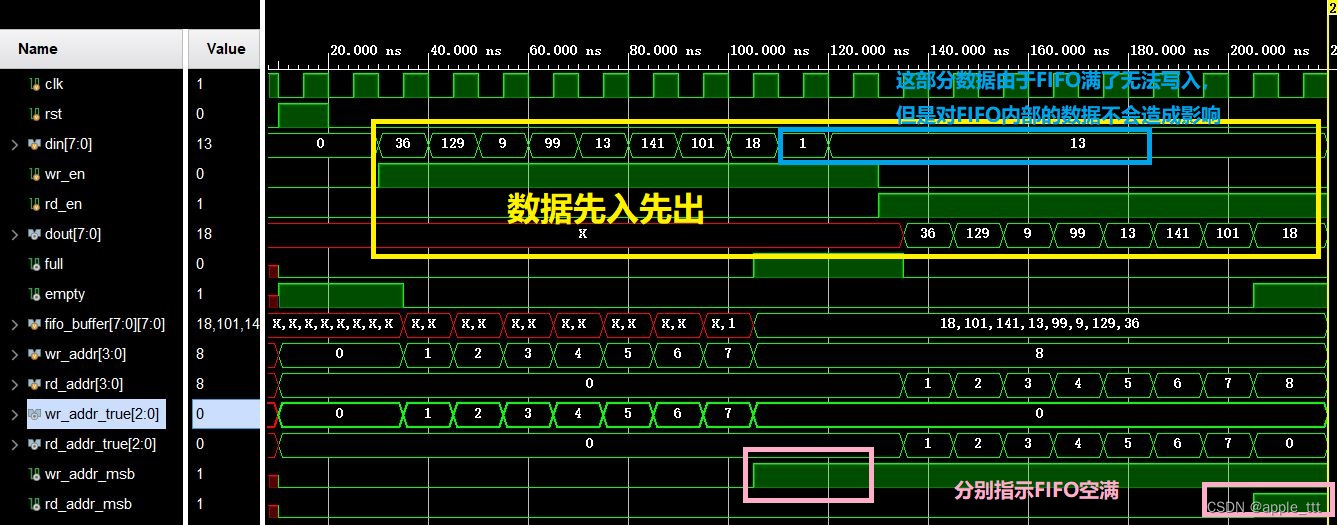

【FIFO】Standard / FWFT FIFO设计实现(二)——异步时钟

标准FIFO 异步FIFO需要使用格雷码同步读写信号,可参考牛客异步FIFO例题,不同于牛客例题之处在于FIFO读空信号置位与FIFO最后一个有效数据输出在同一个周期,与Xilinx FIFO一致。核心代码如下: logic [FIFO_DEPTH_WIDTH : 0] rd_ptr…

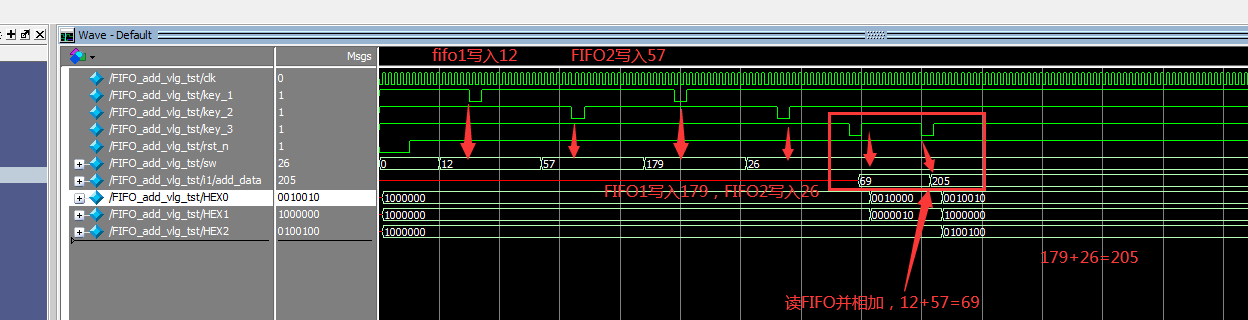

Quartus调用FIFO-IP核verilog,DE1开发板,代码和视频

名称:Quartus调用FIFO-IP核,完成数据的求和

软件:Quartus

语言:Verilog

代码功能:

题目:FIFO-IP核的调用

主要内容:调用两个FIFO-IP核,完成2行数据的求和

技术参数:…

FIFO设计16*8,verilog,源码和视频

名称:FIFO设计16*8,数据显示在数码管

软件:Quartus

语言:Verilog

代码功能:

使用verilog语言设计一个16*8的FIFO,深度16,宽度为8。可对FIFO进行写和读,并将FIFO读出的数据显示到…

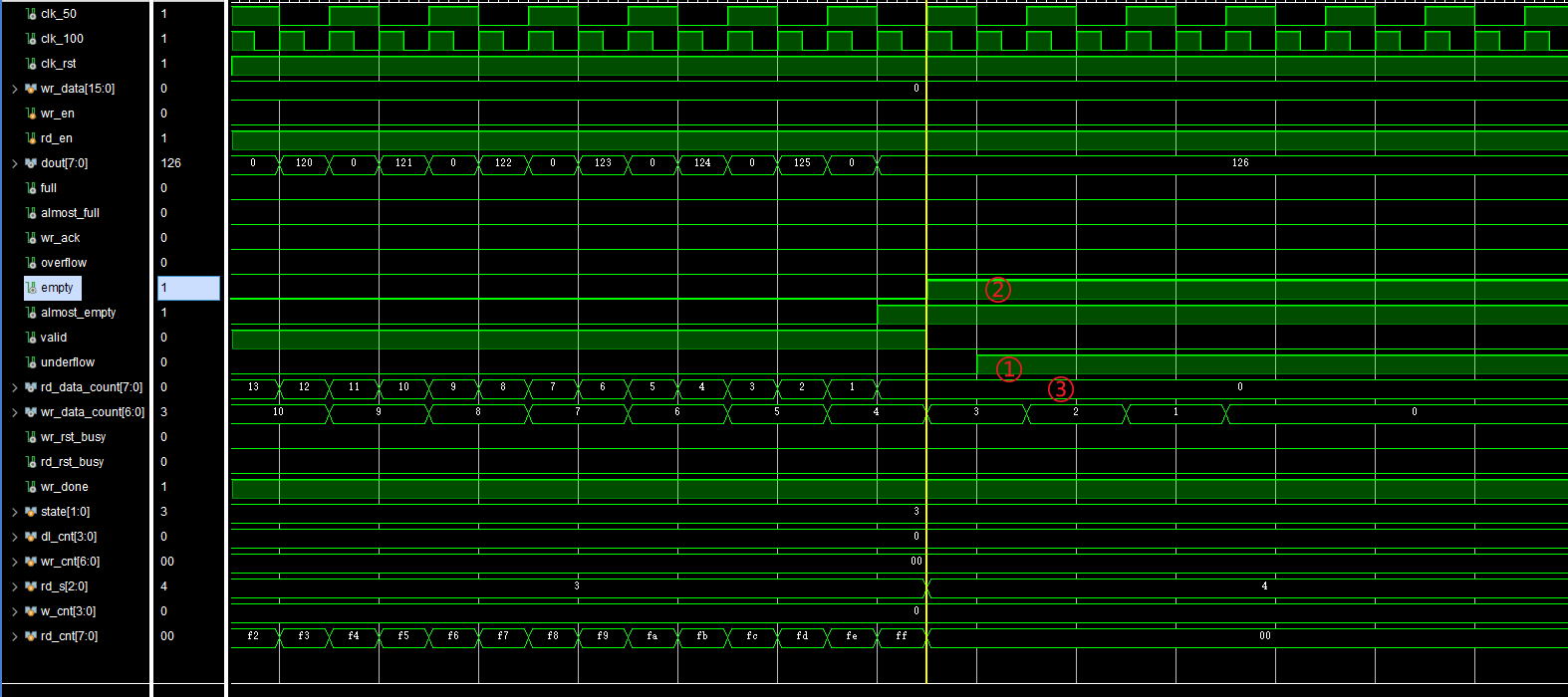

FPGA原理与结构——FIFO IP核的使用与测试

一、前言 本文介绍FIFO Generator v13.2 IP核的具体使用与例化,在学习一个IP核的使用之前,首先需要对于IP核的具体参数和原理有一个基本的了解,具体可以参考:

FPGA原理与结构——FIFO IP核原理学习https://blog.csdn.net/apple_5…

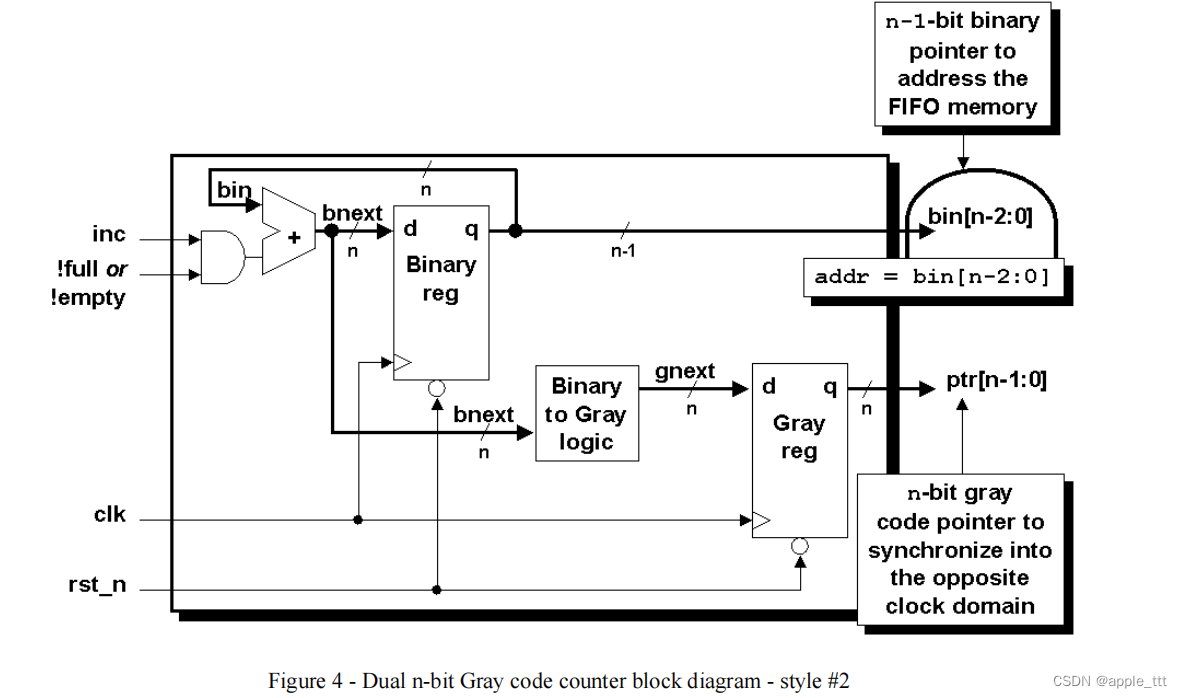

异步FIFO设计的仿真与综合技术(2)

概述 本文主体翻译自C. E. Cummings and S. Design, “Simulation and Synthesis Techniques for Asynchronous FIFO Design 一文,添加了笔者的个人理解与注释,文中蓝色部分为笔者注或意译。前文链接:异步FIFO设计的仿真与综合技术࿰…

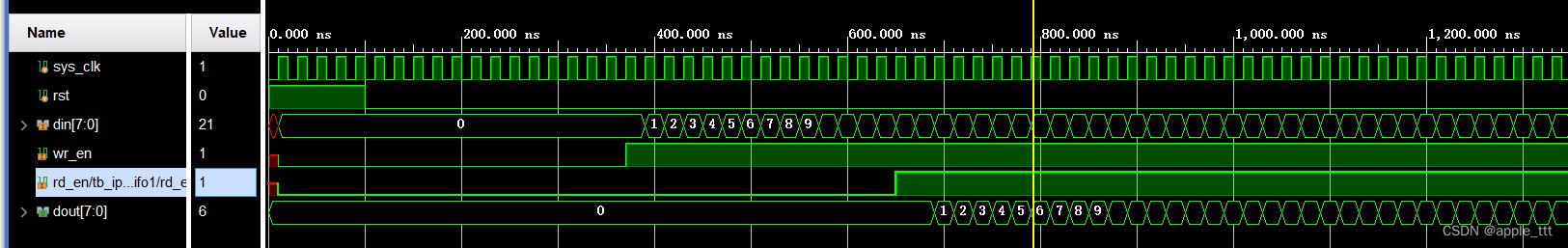

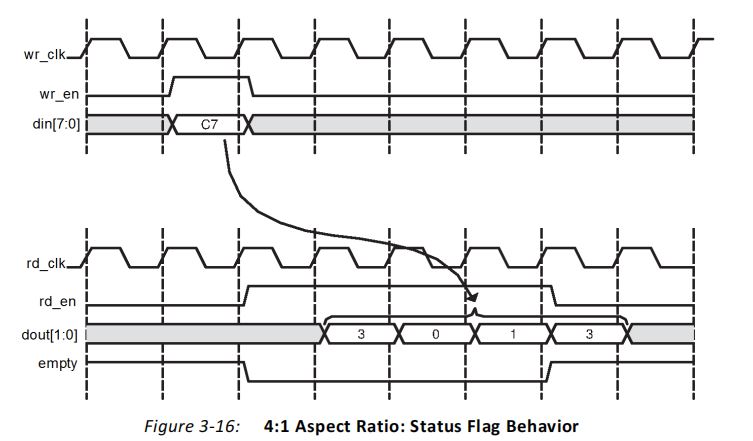

Verilog功能模块——标准FIFO转FWFT FIFO

前言 在使用FIFO IP核时,我更喜欢使用FWFT(First Word First Through) FIFO而非标准FIFO,FWFT FIFO的数据会预先加载到dout端口,当empty为低时数据就已经有效了,而rd_en信号是指示此FIFO更新下一个数据,这种FWFT FIFO的…

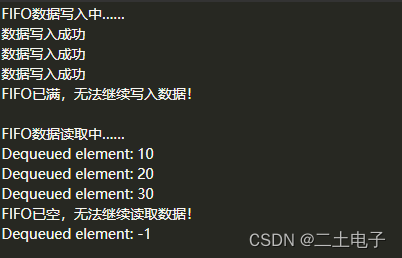

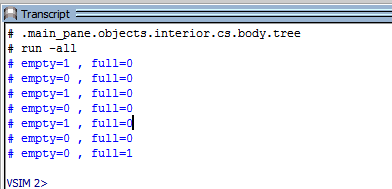

kubernetes之client-go基础包fifo和delta_fifo

目录

直奔主题

FIFO和delta_FIFO抽象

FIFO实现

结构及初始化(调度器用到这个队列)

重要方法介绍

DELTA_FIFO实现

其他几个类型说明

结构及初始化

重要方法介绍

DeltaFIFO创建对象键函数

基础方法

总结

参考 直奔主题

FIFO和delta_FIFO抽象

// Queue is exactly …

G2—FIFO IP核2023-04-07

1.简介

FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,fifo在FPGA内部是RAM加上已编写好的读写控制模块(RTL级)然后“封装”在一起的一个module。他与普通存储器的区别是没有外部读写地址线,这样使…

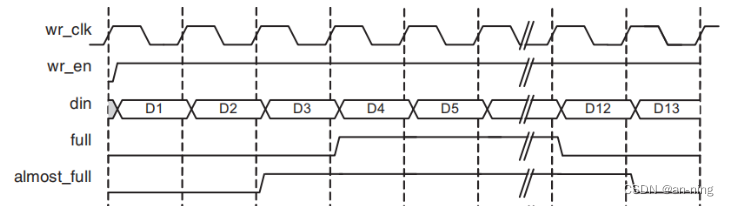

Vavido IP核Independent Clocks Block RAM FIFO简述

文章目录 1 FIFO(先入先出)1.1 概念1.2 应用场景1.3 FIFO信号1.4 FIFO读写时序1.4.1 FIFO读时序1.4.2 FIFO写时序 参考 1 FIFO(先入先出)

1.1 概念 FIFO(First in First out)即先入先出队列,是…

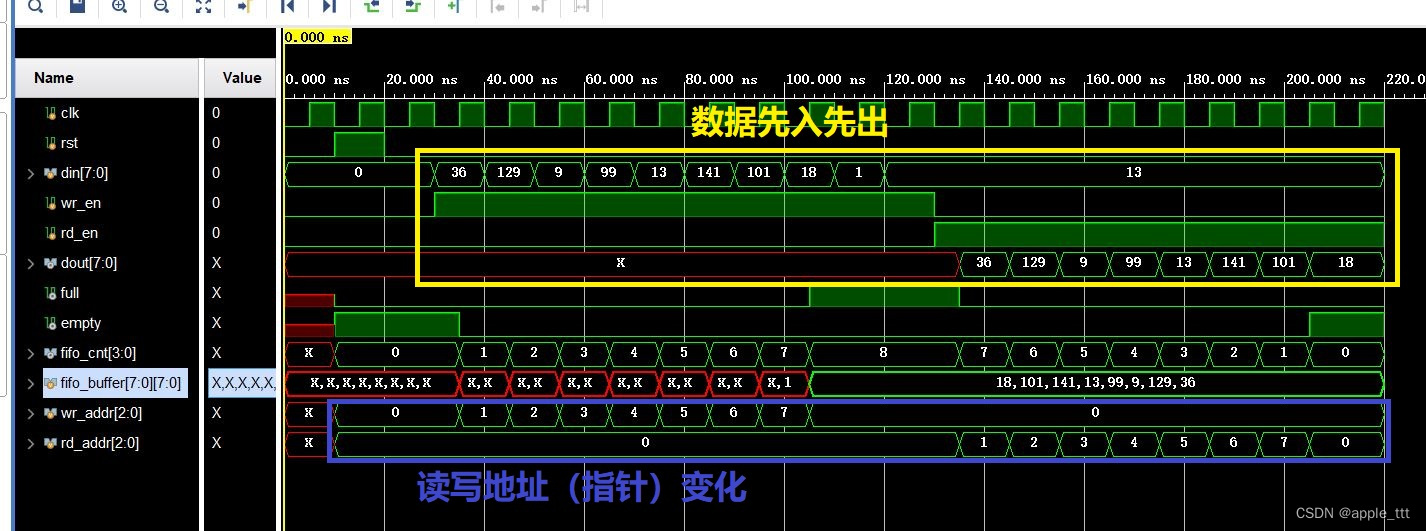

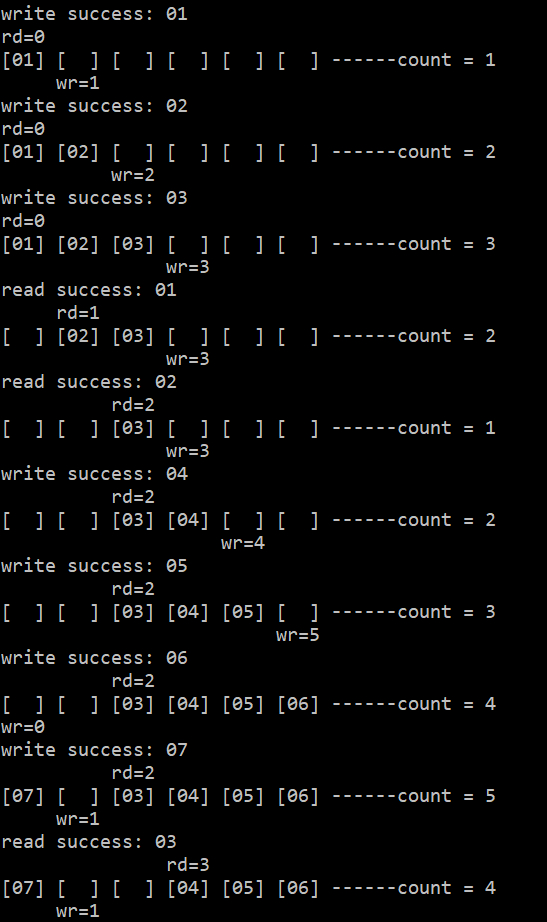

同步FIFO的verilog实现(1)——计数法

一、FIFO概述

1、FIFO的定义 FIFO是英文First-In-First-Out的缩写,是一种先入先出的数据缓冲器,与一般的存储器的区别在于没有地址线, 使用起来简单,缺点是只能顺序读写数据,其数据地址由内部读写指针自动加1完成&…

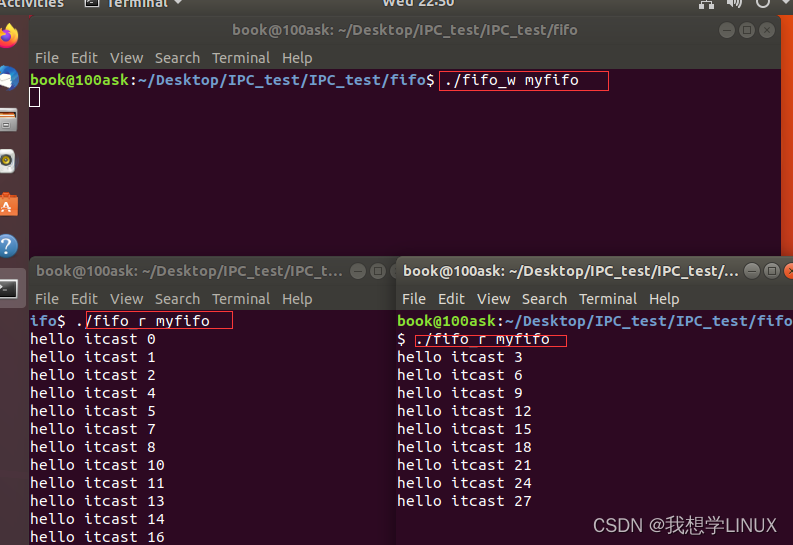

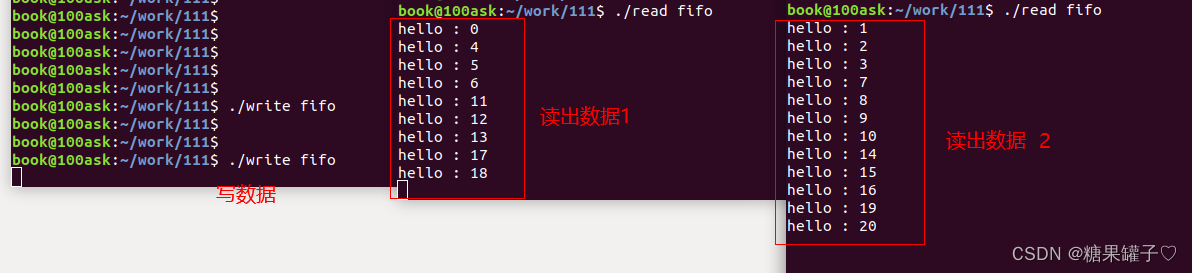

Linux下的系统编程——进程间的通信(九)

前言:

前面我们已经对进程已经有了一个简单的了解与认识,那么进程间的通信是什么样的呢,什么是父子进程,什么是兄弟进程,没有血缘关系间的进程是如何实现进程通信的,下面让我们一起学习一下什么是进程间的…

通用FIFO设计深度8宽度64,verilog仿真,源码和视频

名称:通用FIFO设计深度8宽度64,verilog仿真

软件:Quartus

语言:verilog

本代码为FIFO通用代码,其他深度和位宽可简单修改以下参数得到

reg [63:0] ram [7:0];//RAM。深度8,宽度64

代码功能:…

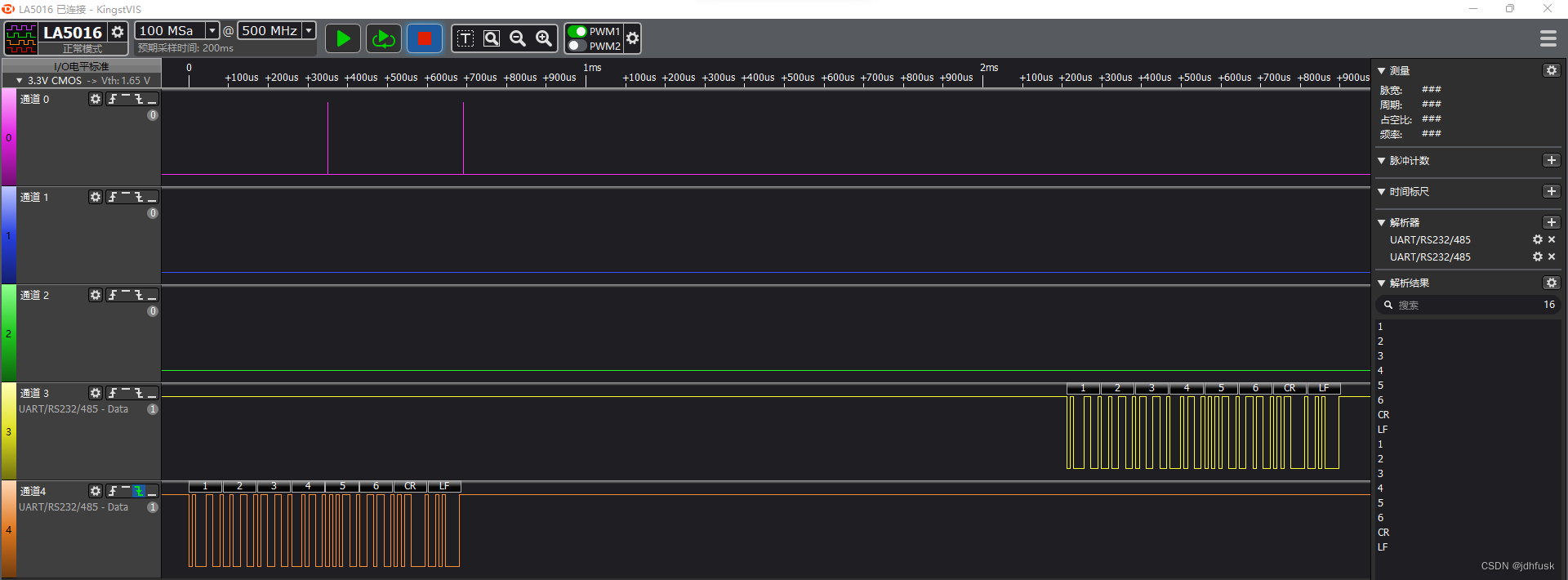

stm32 串口+DMA+环形FIFO缓存收发数据

μcos环境例程 freertos环境例程 重要几点 1.配置DMA,串口及环形buff之间的关系; 2.USART_IT_IDLE空闲中断接收完一帧数据,处理环形buff入口指针,通知用户程序接收完一次数据; 3.发送数据无需利用环形buff,直接将待传数…

《Clock Domain Crossing》 翻译与理解(5)多信号跨时钟域传输

本系列将对sunburst design网站的2008最佳文章《Clock Domain Crossing (CDC) Design & Verification Techniques Using SystemVerilog》进行翻译和基于自我理解的分析阐述,本文介绍多信号跨时钟域传输。

目录

多信号跨时钟域传输

多比特 CDC策略

多比特信号…

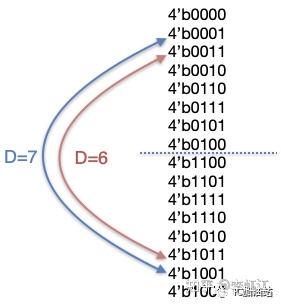

跨时钟域异步FIFO设计verilog(二)异步FIFO设计

三、设计要点解析

1、读空信号如何产生?写满信号如何产生? 读空信号:复位的时候,读指针和写指针相等,读空信号有效(这里所说的指针其实就是读地址、写地址) 当读指针赶上写指针的时候ÿ…

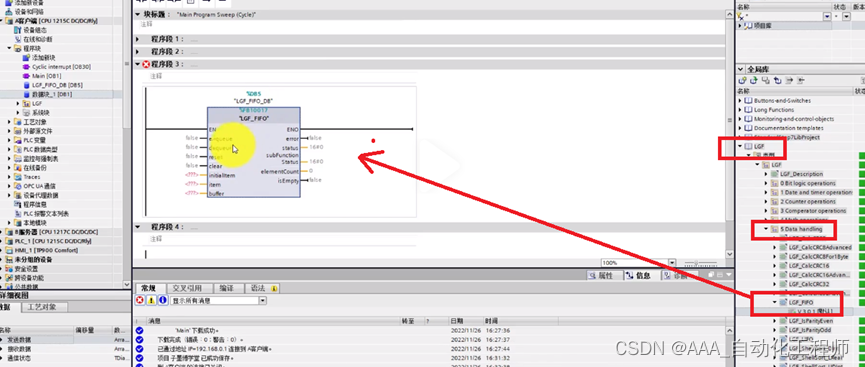

TIA博途中通用函数库指令FIFO先入先出的具体使用方法

TIA博途中通用函数库指令FIFO先入先出的具体使用方法 前些天发现了一个巨牛的人工智能学习网站,通俗易懂,风趣幽默,忍不住分享一下给大家。点击跳转到网站。

如下图所示,在TIA博途中添加通用函数库指令,然后在库指令中找到FIFO,鼠标直接拖拽到程序段中,系统会自动生成一…

Designing_With_EZ-USB_FX2LP_Slave_FIFO_Interface-Source Code_Verilog——Stream In

(1)fx2lp_slaveFIFO2b_streamIN_fpga_top.v

module fx2lp_slaveFIFO2b_streamIN_fpga_top(

// reset_n,fdata, faddr, slrd, slwr, sloe, flagd, flaga, clk, clk_out,pkt_end,done,sync,dbug_sig

);//input reset_n;

inout [15:0]fdata;

input fla…

跨时钟域异步FIFO设计verilog(一)FIFO原理介绍

本文大部分内容来自https://www.cnblogs.com/aslmer/p/6114216.html

本文首先对异步 FIFO 设计的重点难点进行分析 最后给出详细代码 设计一个异步FIFO,深度为8,位宽也是8. 代码是学习Simulation and Synthesis Techniques for Asynchronous FIFO Desig…

AX7A200教程(6): 串口接收图片数据,通过hdmi接口输出显示

本章节主要使用uart接收图片数据,然后通过ddr3缓存,最后通过hdmi接口显示输出,功能框图如下图所示 uart接收的图片数据位1024*768*3分辨率大小的数据,一共2359296个字节,输入图片如下图所示 图片属性 串口接收数据&…

AX7A200教程(4): DDR3的读写fifo仿真

在上篇博客中,我们只是进行突发读写,没有使用读写fifo对ddr3进行读写,因ddr3读写接口都是256位宽,所以ddr3的读写fifo输入和输出都是32位,和ddr3对接的接口都是256位,如下面示意图所示。下面的截图为ddr3的…

Linux命名管道进程通信

文章目录 前言一、什么是命名管道通信二、创建方式三、代码示例四、文件进程通信总结 前言

命名管道 是实现进程间通信的强大工具,它提供了一种简单而有效的方式,允许不同进程之间进行可靠的数据交换。不仅可以在同一主机上的不相关进程间进行通信&…

进程间通信,有名管道(pipe)与无名管道(fifo)的解析与运用,以及代码实现

🎊【进程通信与并发】专题正在持续更新中,进程,线程,IPC,线程池等的创建原理与运用✨,欢迎大家前往订阅本专题,获取更多详细信息哦🎏🎏🎏 🪔本系列…

Actel---ProASIC®3 Flash Family FPGAs with Optional Soft ARM® Support

ProASIC3 Flash Family FPGAs with Optional Soft ARM Support

Features and Benefits High Capacity • 30 k to 1 Million System Gates • Up to 144 kbits of True Dual-Port SRAM • Up to 300 User I/Os Reprogrammable Flash Technology • 130-nm, 7-Layer Metal (6 C…

Emmc系列(一)--------基本概念

目录

1. 名词解释

2. 系统框架 3. 模块 3.1 Emmc控制器 3.2 Emmc设备

4. 总结 1. 名词解释 Emmc:Embedded Multi-Media Card,嵌入式多媒体卡。

在工程技术领域,会引入Emmc设备、Emmc控制器、Emmc协议这些概念。 Emmc设备:遵循…

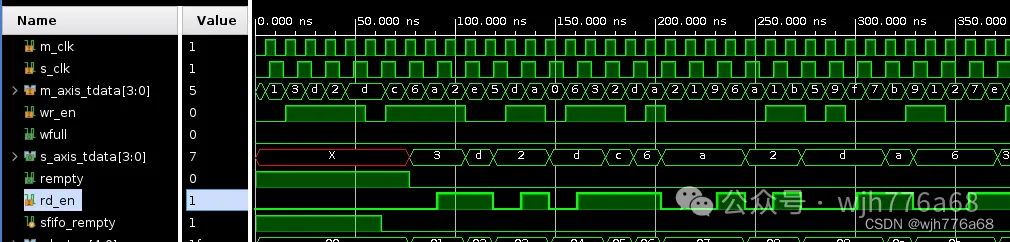

【AXIS】AXI-Stream FIFO设计实现(四)——异步时钟

前文介绍了几种同步时钟情况下的AXI Stream FIFO实现方式,一般来说,FIFO也需要承担异步时钟域模块间数据传输的功能,本文介绍异步AXIS FIFO的实现方式。 如前文所说,AXI-Stream FIFO十分类似于FWFT异步FIFO,推荐参考前…

linux进程间通信之------管道、命名管道

管道

概述

管道是一种两个进程间进行单向通信的机制。因为管道传递数据的单向性,管道又称为半双工管道。

管道的这一特点决定了器使用的局限性。管道是Linux支持的最初Unix IPC形式之一,shell中管道符“|”及tee命令就用到了管道。具有以下特点&#…

异步FIFO设计的仿真与综合技术(3)

概述 本文主体翻译自C. E. Cummings and S. Design, “Simulation and Synthesis Techniques for Asynchronous FIFO Design 一文,添加了笔者的个人理解与注释,文中蓝色部分为笔者注或意译。前文链接:

异步FIFO设计的仿真与综合技术…

linux系统编程:进程间通信-fifo

进程间通信-fifo

进程间通信的另一种方式是fifo。fifo是另一种管道:有名管道。从名字可以看出,它也是队列。

使用fifo通信前,得先创建fifo$ mkfifo myfifo随后只需对myfifo像文件一样使用就行。

fifo_w.c#include <stdio.h>

#include &…

xqueue:基于C语言实现的循环队列缓冲区

文章目录1. 为什么需要FIFO2. FIFO的存取顺序3. FIFO的代码实现4. 开源地址精选1. 为什么需要FIFO

FIFO 是First-In First-Out的缩写,它是一个具有先入先出特点的缓冲区。

可以理解成一个大的水池,水对应数据,注水速度对应数据输入的频率&a…

Verilog功能模块——同步FIFO

前言 FIFO功能模块分两篇文章,本篇为同步FIFO,另一篇为异步FIFO,传送门:

Verilog功能模块——异步FIFO-CSDN博客

同步FIFO实现起来是异步FIFO的简化版,所以,本博文不再介绍FIFO实现原理,感兴趣…

进程间通信 - 管道

现今常用的进程间通信方式有:

管道(使用最简单)信号(开销最小)共享内存(无血缘关系)套接字(最稳定)

管道的概念 这里指命名管道,管道是一种最基本的IPC机制…

FIFO设计核心问题

1.什么是FIFO?

FIFO (First-In-First-Out) 是一种先进先出的数据交互方式,在数字ASIC设计中常常被使用。FIFO按工作时钟域的不同又可以分为:同步FIFO和异步FIFO。

使用异步FIFO可以在两个不同的时钟域之间快速而方便的传输数据,…

同步FIFO的verilog实现(2)——高位扩展法

一、前言 在之前的文章中,我们介绍了同步FIFO的verilog的一种实现方法:计数法。其核心在于:在同步FIFO中,我们可以很容易的使用计数来判断FIFO中还剩下多少可读的数据,从而可以判断空、满。 关于计数法实现同步FIFO的详…

FPGA原理与结构——FIFO IP核原理学习

一、FIFO概述

1、FIFO的定义 FIFO是英文First-In-First-Out的缩写,是一种先入先出的数据缓冲器,与一般的存储器的区别在于没有地址线, 使用起来简单,缺点是只能顺序读写数据,其数据地址由内部读写指针自动加1完成&…

异步FIFO设计的仿真与综合技术(6)

概述 本文主体翻译自C. E. Cummings and S. Design, “Simulation and Synthesis Techniques for Asynchronous FIFO Design 一文,添加了笔者的个人理解与注释,文中蓝色部分为笔者注或意译。前文链接:

异步FIFO设计的仿真与综合技术…

FPGA的通用FIFO设计verilog,1024*8bit仿真,源码和视频

名称:FIFO存储器设计1024*8bit

软件:Quartus

语言:Verilog

本代码为FIFO通用代码,其他深度和位宽可简单修改以下参数得到

reg [7:0] ram [1023:0];//RAM。深度1024,宽度8

代码功能:

设计一个基于FPGA…

记录一次对STM32G4串口硬件FIFO的调试

记录一次对STM32G4串口硬件FIFO的调试 前言:通常我们使用串口接收多字节数据会使用中断和DMA两种方式。使用中断方式,每接收到一个字节就会触发一次中断,我们可以在中断函数里将接收到的这一字节保存在内存中然后等待其他程序处理,…

Ehcache源码解析——缓存淘汰机制

一、Ehcache淘汰机制

下面是Ehcache淘汰机制时序图: Ehcache缓存淘汰时,主要做了下面几件事情:

put操作结束后,判断是否超出了最大容量从SelectableConcurrentHashMap中随机取出不超过30个元素作为淘汰样本根据淘汰策略选出样本…

数据结构和算法专题---3、失效算法与应用

本章我们会对失效算法做个简单介绍,包括常用的失效算法(先来先淘汰(FIFO)、最久未用淘汰(LRU)、最近最少使用(LFU))的概述、实现方式、典型场景做个说明。

什么是失效算…